# **OKI** Semiconductor

# **MSC1157**

Speaker Drive Amplifier

# GENERAL DESCRIPTION

The MSC1157, designed specifically to operate at a low voltage with low current consumption, is a power amplifier developed for driving a speaker for a voice IC.

The voltage gains can be adjusted over a range of up to ten. The differential output can directly drive a speaker without any output coupling capacitors. The MSC 1157, because of its ability to stand by, is ideally suitable for portable equipment applications powered by a battery.

# **FEATURES**

• Low voltage operation

• Low current dissipation Operating current

Standby function

High output current

• Differential outputs

Adjustable gain

Package options:

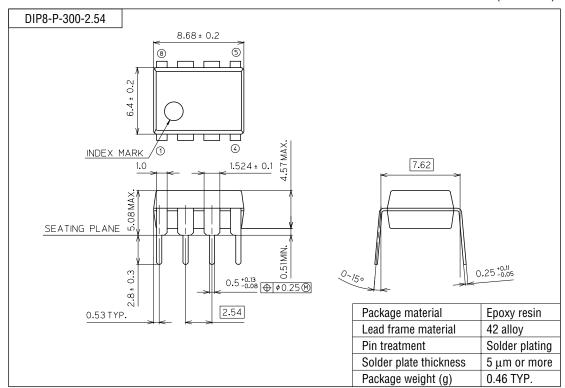

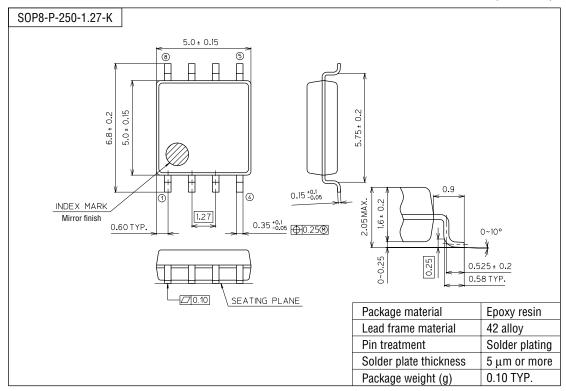

8-pin plastic DIP (DIP8-P-300-2.54) 8-pin plastic SOP (SOP8-P-250-1.27-K) (Product name: MSC1157MS-K)

Chip

: 2.0 to 6.0 V (Single power supply)

: 1.6mA without load (typ.)

: Current dissipation less than 1 μA in standby

This version: Feb. 1999

Previous version: May. 1997

: 350mA peak

: A speaker can be directly connected between

differential outputs.

(Product name: MSC1157RS)

: Gain can be adjusted by use of an external resistor.

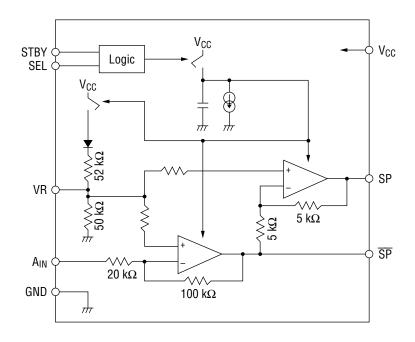

# **BLOCK DIAGRAM**

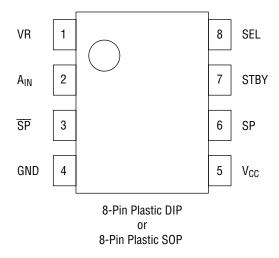

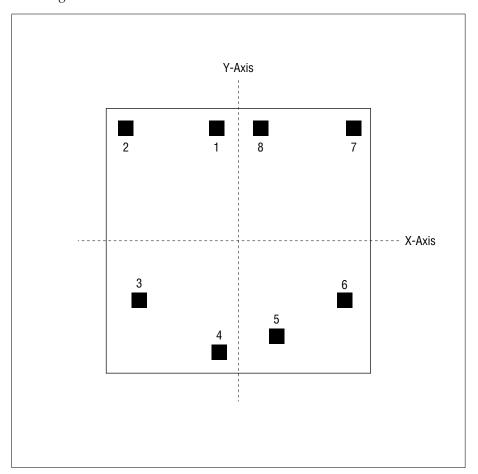

# PIN CONFIGURATION (TOP VIEW)

# **PIN DESCRIPTIONS**

| Pin  | Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                                  |                                                                                    |                                                                                                                                                                      |  |  |  |

|------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5    | $V_{CC}$        | _    | Power supply pin.                                                                                                                                                                                                                                                                                                            |                                                                                    |                                                                                                                                                                      |  |  |  |

| 4    | GND             | _    | Ground pin.                                                                                                                                                                                                                                                                                                                  |                                                                                    |                                                                                                                                                                      |  |  |  |

| 2    | A <sub>IN</sub> | I    | Signal input pin for analog signal inputs, etc.                                                                                                                                                                                                                                                                              |                                                                                    |                                                                                                                                                                      |  |  |  |

| 7, 8 | STBY,<br>SEL    | I    | Digital input pins. Setting these pins configures for how to set the pins.  SEL  0  1  Clock  Applying a clock between 32kHz and 4MHz to eit to operation status regardless of the status set a of the pins at the same time may cause malfunc Refer to the section, RECOMMENDED OPERATI are changed by setting the SEL pin. | STBY  0  1 Clock  0 1 Clock  0 1 Clock  ther the STBY or the at the other pin. App | Status Operation Standby Operation Standby Operation Operation Operation Operation Unstable Operation SEL pin leads the IC lying clocks to both ce clock frequencies |  |  |  |

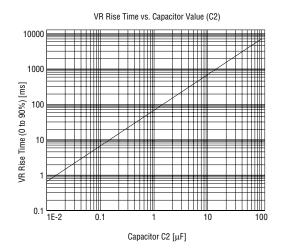

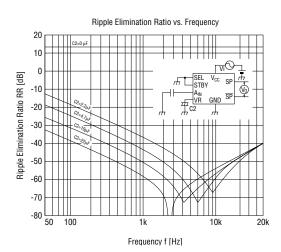

| 1    | VR              | 0    | Bias output pin for internal circuits. This pin is at GND potential during standby.  Connecting a capacitor between VR and the GND pin reduces the pop-up noise at power on and improves the ripple elimination ratio.                                                                                                       |                                                                                    |                                                                                                                                                                      |  |  |  |

| 3    | SP              | 0    | Speaker output pin. This pin outputs a negative phase with respect to the input signal.                                                                                                                                                                                                                                      |                                                                                    |                                                                                                                                                                      |  |  |  |

| 6    | SP              | 0    | Speaker output pin. This pin outputs a positive phase with respect to the input signal.                                                                                                                                                                                                                                      |                                                                                    |                                                                                                                                                                      |  |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter              | Symbol            | Condition | Rating                       | Unit | Remark                |

|------------------------|-------------------|-----------|------------------------------|------|-----------------------|

| Power Supply Voltage   | Vcc               | Ta=25°C   | -0.3 to +6.5                 | V    | $V_{CC}$              |

| Innut Voltage          | ,                 | Ta=25°C   | 0.04-1/ .0.0                 | V    | STBY                  |

| Input Voltage          | V <sub>IN</sub>   |           | –0.3 to V <sub>CC</sub> +0.3 |      | A <sub>IN</sub> , SEL |

| Maximum Output Current |                   | Ta=25°C   | (*1)                         |      |                       |

| Maximum Output Current | IOMAX             |           | ±400                         | mA   | $SP, \overline{SP}$   |

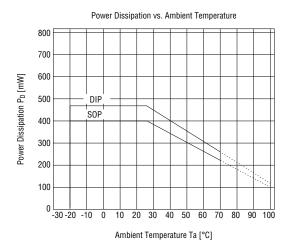

| Dawar Dissination      | _ n               | To 0590   | 470                          | mW   | DIP type              |

| Power Dissipation      | P <sub>D</sub>    | Ta=25°C   | 400                          | mW   | SOP type              |

| Junction Temperature   | T <sub>jMAX</sub> | _         | 125                          | °C   | Chip                  |

| Storage Temperature    | T <sub>STG</sub>  | <u> </u>  | −55 to +150                  | °C   |                       |

<sup>\*1</sup> Avoid shorting the output pins (SP and  $\overline{SP}$ ) to  $V_{CC}$  or GND because the IC may be damaged.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                     | Symbol           | Condition                  | Min.                | Max.                | Unit |

|-------------------------------|------------------|----------------------------|---------------------|---------------------|------|

| Power Supply Voltage          | V <sub>CC</sub>  | _                          | 2.0                 | 6.0                 | V    |

| Load Impedance (*2)           | RL               | _                          | 8.0                 |                     | Ω    |

| Peak Load Current             | I <sub>0-P</sub> | _                          | <u> </u>            | 350                 | mA   |

| "H" Input Voltage             | V <sub>IH</sub>  | For STBY and SEL pins      | 0.7 V <sub>CC</sub> | _                   | V    |

| "L" Input Voltage             | V <sub>IL</sub>  | FUI STET AIIU SEL PIIIS    | _                   | 0.3 V <sub>CC</sub> | V    |

|                               |                  | SEL = "L"                  |                     | 4.096 M             | - Hz |

|                               | <b>f</b> .       | At clock input             | 32 k                |                     |      |

| CTDV Operating Frequency (*2) |                  | $V_{CC} \ge 2.4 \text{ V}$ |                     |                     |      |

| STBY Operating Frequency (*3) | TSTBY            | SEL = "H"                  |                     |                     |      |

|                               |                  | At clock input             | 32 k                | 1 M                 |      |

|                               |                  | $V_{CC} \ge 2.4 \text{ V}$ |                     |                     |      |

| Operating Temperature         | Тор              | _                          | -20                 | +70                 | °C   |

<sup>\*2</sup> A speaker of 8  $\Omega$  (standard) or more should be used.

<sup>\*3</sup> The input of clocks may cause a little noise in output waveforms. It is recommended to input the DC voltage to inprove voice quality.

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, Ta=25°C, V<sub>CC</sub>=2 to 6 V

| Unitess utiletwise specified, Ta=25 G, VCC=2 to 0 V |                                                          |                                                                      |                                |                       |                       |       |      |

|-----------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|--------------------------------|-----------------------|-----------------------|-------|------|

| Parameter                                           | Symbol                                                   | l Condition                                                          |                                | Min.                  | Тур.                  | Max.  | Unit |

| A <sub>IN</sub> Input Resistance                    | R <sub>IN</sub>                                          | _                                                                    |                                | 14                    | 20                    | 26    | kΩ   |

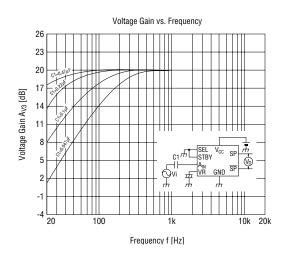

|                                                     | A <sub>V1</sub>                                          | A <sub>II</sub>                                                      | $_{N}\rightarrow\overline{SP}$ | 13.44                 | 14                    | 14.49 |      |

| Voltage Gain                                        | A <sub>V2</sub>                                          | <del>SP</del> →SP                                                    |                                | -1.94                 | 0                     | +1.58 | dB   |

|                                                     | A <sub>V3</sub>                                          | A <sub>IN</sub> →(Between <del>SP</del> -SP)                         |                                | 19.46                 | 20                    | 20.51 |      |

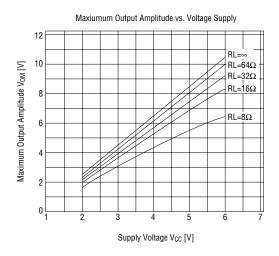

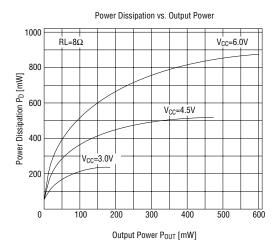

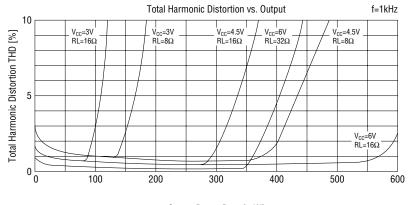

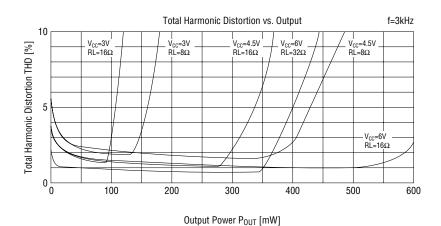

| Output Dovor                                        | P <sub>OUT1</sub>                                        | V <sub>CC</sub> =3 V, f=1 kHz<br>RL=8 Ω, THD≥10%                     |                                | 100                   | 178                   | _     | mW   |

| Output Power                                        | P <sub>OUT2</sub>                                        | V <sub>CC</sub> =6 V, f=1 kHz<br>RL=32 Ω, THD≥10%                    |                                | 300                   | 440                   | _     | mW   |

| Tatal Harmania Distantian                           | THD1                                                     | $V_{CC}$ =3 V, RL=8 $\Omega$<br>f=1 kHz, $P_{OUT}$ =45 mW            |                                | _                     | 1.2                   | _     | %    |

| Total Harmonic Distortion                           | THD2                                                     | $V_{CC}$ =6 V, RL=32 $\Omega$<br>f=1 kHz, $P_{OUT}$ =125 mW          |                                | _                     | 0.37                  | _     | %    |

| Ripple Elimination Ratio                            | RR                                                       | f=1 kHz, C2=4.7 μF                                                   |                                | 30                    | 43                    | _     | dB   |

| Output DC Voltage                                   | .,,                                                      | In no<br>signal state                                                | V <sub>CC</sub> =2 V           | 0.53                  | 0.65                  | 0.77  | V    |

| (*4)                                                | V <sub>0</sub>                                           |                                                                      | V <sub>CC</sub> =6 V           | 2.49                  | 2.61                  | 2.73  |      |

| Output Offset Voltage                               | ΔV <sub>0</sub>                                          | Between SP-SP                                                        |                                | _                     | _                     | ±30   | mV   |

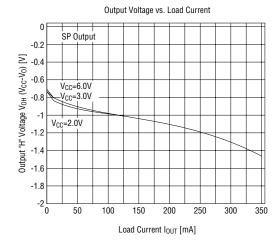

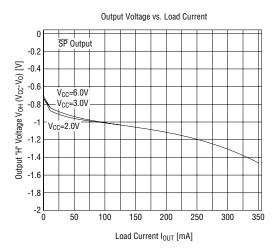

| Output "H" Voltage                                  | V <sub>OH</sub>                                          | A <sub>IN</sub> =V <sub>CC</sub> or GND<br>I <sub>OUT</sub> =-100 mA |                                | V <sub>CC</sub> -1.15 | V <sub>CC</sub> -1.04 | _     | V    |

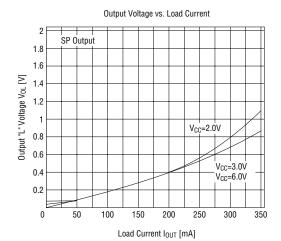

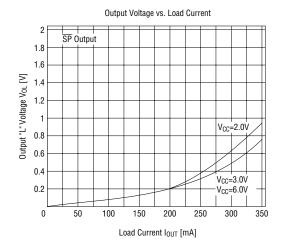

| Output "L" Voltage                                  | Voltage $V_{OL}$ $A_{IN}=V_{CC}$ or GND $I_{OUT}=100$ mA |                                                                      | _                              | 0.17                  | 0.3                   | V     |      |

| STBY, SEL                                           | I <sub>IH</sub>                                          | V <sub>I</sub> =V <sub>CC</sub>                                      |                                | _                     | _                     | ±0.1  | μA   |

| Input Current                                       | I <sub>IL</sub>                                          | V <sub>I</sub> =GND                                                  |                                | _                     | _                     | ±0.1  | μΑ   |

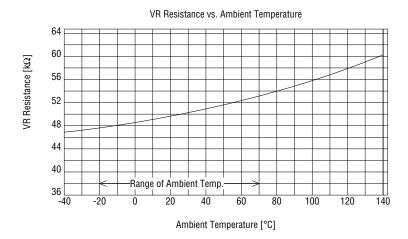

| VR Equivalent Resistance                            | R <sub>VR</sub>                                          | _                                                                    |                                | 18                    | 25                    | 32    | kΩ   |

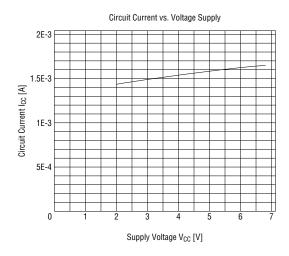

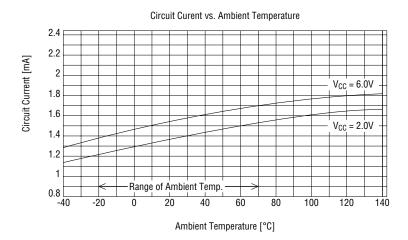

| Circuit Current During Operation                    | I <sub>CC</sub>                                          | V <sub>CC</sub> =6 V, RL=∞                                           |                                | 1.1                   | 1.6                   | 2.4   | mA   |

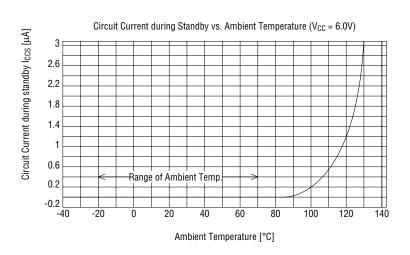

| Circuit Current During Standby                      | Iccs                                                     | _                                                                    |                                | _                     | _                     | 1.0   | μА   |

<sup>\*4</sup> The typical value of the output voltage in no signal state is determined from the following equation.

$$V_{O} = (V_{CC} - 0.67) \frac{50 \text{ k}\Omega}{50 \text{ k}\Omega + 52 \text{ k}\Omega}$$

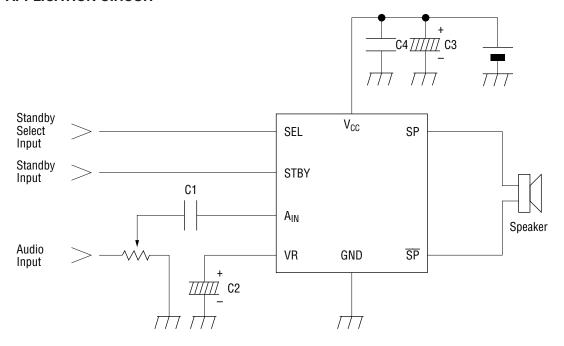

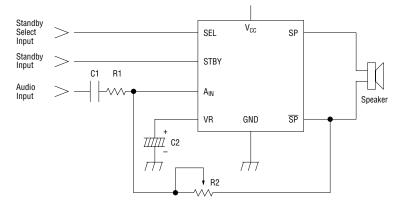

### **APPLICATION CIRCUIT**

- If parasitic capacitance of 60pF or more exists between GND and the speaker output pin  $\overline{SP}$  or  $\overline{SP}$ , oscillation may occur. Implement the circuit mount design so as to be less than 60pF.

- C1 is the AC coupling capacitor. Cutoff frequency fc on the low frequency side is determined by the following equation. Choose a value of C1 according to the bandwidth.

$$fc = \frac{1}{2 \times \pi \times C1 \times 20k} \quad (Hz)$$

- Choose a value of C2 that is 80 to 100 times as large as that of C1.

- $\bullet$  When the standby function is not used, connect the pins STBY and SEL to  $V_{CC}$  or GND.

- It is recommended that the capacitor C4 (approximately  $0.1\mu F$ ) having better high frequency characteristics and the capacitor C3 (approximately  $10\mu F$ ) be placed between the pins  $V_{CC}$  and GND.

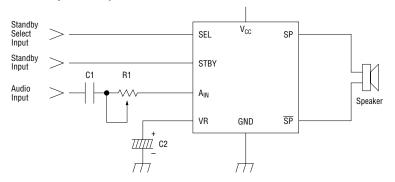

### **GAIN ADJUSTMENT**

Gain Adjustment Using Input Resistance (This approach allows gain adjustment with fewer external components)

• Cutoff frequency fc on the low frequency side is determined from the equation:

$$fc = \frac{1}{2 \times \pi \times C1 \times (R1 + 20k)}$$

(Hz)

• Voltage gain A<sub>V1</sub> is determined from the equation:

$$A_{V1} \doteq \frac{100k}{R1 + 20k} (V/V)$$

2. Gain Adjustment Using Feedback Resistance (This approach has the advantage over the above approach (less noise approach), but the number of components is increased)

• Cutoff frequency fc on the low frequency side is determined from the equation:

fc

$$=$$

$\frac{1}{2 \times \pi \times C1 \times Zin}$  (Hz)  $Zin = R1 + \frac{R2 \times 20k}{R2 + 120k}$  ( $\Omega$ )

• Voltage gain  $A_{V1}$  is determined from the equation:

$$A_{V1} = \frac{5}{1 + \frac{R1}{20k} + \frac{6 \times R1}{R2}} (V/V)$$

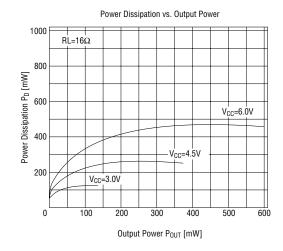

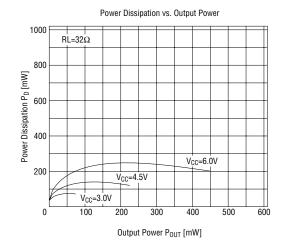

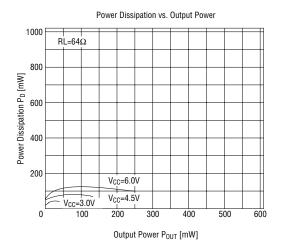

# **OPERATING CHARACTERISTICS**

Output Power Pout [mW]

# **PAD CONFIGURATION**

# **Pad Layout**

Chip size : X=2.3mm, Y=2.4mm

Chip thickness  $:350\pm30\mu m$ Pad size (PV aperture)  $:110\times110\mu m$ Substrate potential :GND

Pad location diagram

# **Pad Coordinates**

(Chip center is located at X=0 and Y=0.)

(Unit: µm)

| Pad Name        | X-AXIS                    | Y-AXIS                                                                                                                                    |  |  |  |  |

|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VR              | -133                      | 1035                                                                                                                                      |  |  |  |  |

| A <sub>IN</sub> | -985                      | 1035                                                                                                                                      |  |  |  |  |

| SP              | -950                      | -263                                                                                                                                      |  |  |  |  |

| GND             | -180                      | -1027                                                                                                                                     |  |  |  |  |

| V <sub>CC</sub> | 240                       | -914                                                                                                                                      |  |  |  |  |

| SP              | 950                       | -263                                                                                                                                      |  |  |  |  |

| STBY            | 985                       | 1035                                                                                                                                      |  |  |  |  |

| SEL             | 159                       | 1035                                                                                                                                      |  |  |  |  |

|                 | VR AIN SP GND Vcc SP STBY | VR     -133       A <sub>IN</sub> -985       SP     -950       GND     -180       V <sub>CC</sub> 240       SP     950       STBY     985 |  |  |  |  |

# **PACKAGE DIMENSIONS**

(Unit: mm)

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, TQFP, LQFP, SOJ, QFJ (PLCC), SHP, and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person on the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.